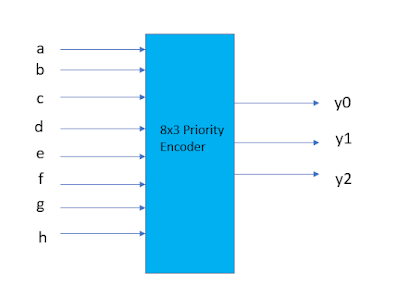

module Priority_8_3 (y2,y1,y0,a,b,c,d,e,f,g,h); input a,b,c,d,e,f,g,h; output reg y2,y1,y0; `ifdef method1 always @* begin case ({a,b,c,d,e,f,g,h}) 8'b11111111: {y2,y1,y0} =3'b111; 8'b11111110: {y2,y1,y0} =3'b111; 8'b11111101: {y2,y1,y0} =3'b111; 8'b11111100: {y2,y1,y0} =3'b111; 8'b11111011: {y2,y1,y0} =3'b111; 8'b11111010: {y2,y1,y0} =3'b111; 8'b11111001: {y2,y1,y0} =3'b111; 8'b11111000: {y2,y1,y0} =3'b111; 8'b11110111: {y2,y1,y0} =3'b111; 8'b11110110: {y2,y1,y0} =3'b111; 8'b11110101: {y2,y1,y0} =3'b111; 8'b11110100: {y2,y1,y0} =3'b111; 8'b11110011: {y2,y1,y0} =3'b111; 8'b11110010: {y2,y1,y0} =3'b111; 8'b11110001: {y2,y1,y0} =3'b111; 8'b11110000: {y2,y1,y0} =3'b111; 8'b11101111: {y2,y1,y0} =3'b111; 8'b11101110: {y2,y1,y0} =3'b111; 8'b11101101: {y2,y1,y0} =3'b111; 8'b11101100: {y2,y1,y0} =3'b111; 8'b11101011: {y2,y1,...