Rational clock divider - Division by 4.5 example

Module :

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Weekendvlsi.blogspot.com

// Engineer: Weekendvlsi

// Create Date:

// Design Name: Rational clock divider - Division by 4.5

// Module Name: clk_div

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// Dependencies:

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module clk_div (clk,rst,clk_4_5);

input clk;

input rst;

output clk_4_5;

reg [8:0] count;

reg SATcount1,SATcount5,SATcount6 ;

/* Counter rst value : 9?b000000001 */

/* count is a ring counter */

always @( posedge clk or posedge rst)

if (rst)

count <='d1;

else

begin

count <= count << 1;

count[0] <= count[8];

end

always @(negedge clk or posedge rst)

if (rst)

begin

SATcount1 <= 1'b0;

SATcount5 <= 1'b0;

SATcount6 <= 1'b0;

end

else

begin

SATcount1 <= count[0];

SATcount5 <= count[4];

SATcount6 <= count[5];

end

// Use this Math to generate an odd clock divider.

assign clk_4_5 = (SATcount5 | SATcount6| count[5])|

(count[0] | count[1] | SATcount1);

endmodule

TESTBENCH

module tb ; reg clk,rst; wire clk_4_5; clk_div weekendvlsi (clk,rst,clk_4_5); initial clk= 1'b0; always #5 clk=~clk; initial begin #6 rst=1'b0; #6 rst=1'b1; #6 rst=1'b0; #1000 $finish; end endmodule

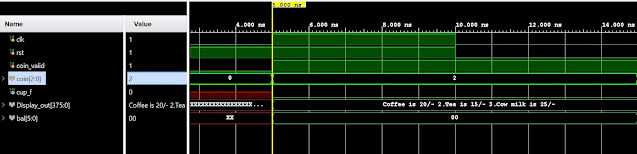

RESULT

Comments

Post a Comment