Different Ways to Design Post Divider

Method -1:

module clk_divider (

input clk,rst,

input [2:0] a,

output reg f2,f4,f8,f16,f32,f64,f128

);

reg [6:0] q;

always@(posedge clk, posedge rst)

begin

if(rst)

f2=1'b0;

else begin

q[0]=~f2;

if(a==3'b001)

f2=q[0];

else

f2=1'b0;

end

end

always@(posedge q[0], posedge rst)

begin

if(rst)

f4=1'b0;

else begin

q[1]=~f4;

if(a==3'b010)

f4=q[1];

else

f4=1'b0;

end

end

always@(posedge q[1], posedge rst)

begin

if(rst)

f8=1'b0;

else begin

q[2]=~f8;

if(a==3'b011)

f8=q[2];

else

f8=1'b0;

end

end

always@(posedge q[2], posedge rst)

begin

if(rst)

f16=1'b0;

else begin

q[3]=~f16;

if(a==3'b100)

f16=q[3];

else

f16=1'b0;

end

end

always@(posedge q[3], posedge rst)

begin

if(rst)

f32=1'b0;

else begin

q[4]=~f32;

if(a==3'b101)

f32=q[4];

else

f32=1'b0;

end

end

always@(posedge q[4], posedge rst)

begin

if(rst)

f64=1'b0;

else begin

q[5]=~f64;

if(a==3'b110)

f64=q[5];

else

f64=1'b0;

end

end

always@(posedge q[5], posedge rst)

begin

if(rst)

f128=1'b0;

else begin

q[6]=~f128;

if(a==3'b111)

f128=q[6];

else

f128=1'b0;

end

end

endmodule

Method -2:

module divide_by_counter(fin, rst,a, y);

input fin, rst;

input [2:0] a;

output y;

reg f2, f4, f8, f16,f32,f64,f128;

reg q1, q2, q3, q4,q5,q6,q7,q0;

assign y=(a==3'b0)?fin:q0;

always @ (posedge fin, posedge rst)

begin

if (rst)begin

{q7,q6,q5,q4,q3,q2,q1}<=7'b0;

{f2, f4, f8, f16,f32,f64,f128}<=7'b0;

end

else

begin

{q7,q6,q5,q4,q3,q2,q1}<={q7,q6,q5,q4,q3,q2,q1}+1'b1;

case(a)

3'b001: begin

f2<=q1;

{f4, f8, f16,f32,f64,f128}<=0;

q0<=f2;

end

3'b010:begin

f4<=q2;

{f2, f8, f16,f32,f64,f128}<=0;

q0<=f4;

end

3'b011: begin

f8<=q3;

{f4, f2, f16,f32,f64,f128}<=0;

q0<=f8;

end

3'b100:begin

f16<=q4;

{f4, f2, f8,f32,f64,f128}<=0;

q0<=f16;

end

3'b101: begin

f32<=q5;

{f4, f2, f8,f16,f64,f128}<=0;

q0<=f32;

end

3'b110: begin

f64<=q6;

{f4, f2, f8,f16,f32,f128}<=0;

q0<=f64;

end

3'b111: begin

f128<=q7;

{f4, f2, f8,f16,f32,f64}<=0;

q0<=f128;

end

default:q0<=1'b0;

endcase

end

end

endmodule

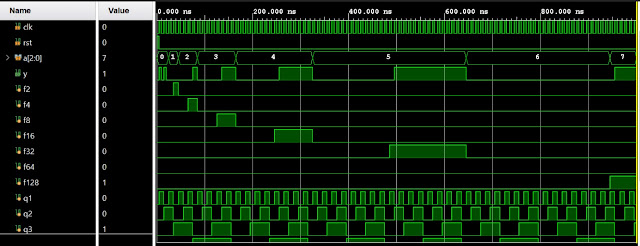

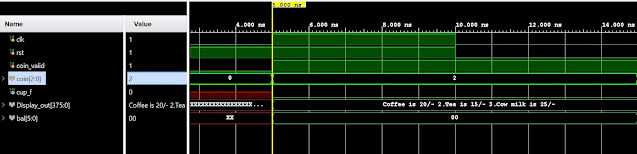

RESULTS:

Comments

Post a Comment