Vending machine Code With Display Options

Vending machine Top Module :

module vending_machine_top (input clk,

input rst,

input coin_valid,

input [2:0] coin,

output cup_f,

output [375:0] Display_out,

output [5:0] bal

);

wire [2:0] w_addr;

vending_machine V1 ( .clk (clk),

.rst (rst),

.coin_valid (coin_valid),

.coin (coin),

.cup_f (cup_f),

.addr (w_addr),

.bal (bal)

);

Display v2 ( .Display_out (Display_out) ,

.addr (w_addr),

.clk (clk)

);

endmodule

Display Module :

module Display(output reg [375:0]Display_out ,input [2:0] addr,clk);

always@(posedge clk)

begin

case(addr)

3'd0 : Display_out<="1.Coffee is 20/- 2.Tea is 15/- 3.Cow milk is 25/-";

3'd1 : Display_out<="Coin is invalid";

3 'd2 : Display_out<="Coffee is filled Please collect coffee";

3'd3 : Display_out<="Please wait coffee is filling";

3'd4 : Display_out<="Tea is filled Please collect Tea";

3 'd5 : Display_out<="Please wait Tea is filling";

3 'd6 : Display_out<="Milk is filled Please collect Milk ";

3'd7 : Display_out<="Please wait Milk is filling";

endcase

end

endmodule

vending machine Module:

module vending_machine( input clk,

input rst,

input coin_valid,

input [2:0] coin,

output reg cup_f, // Cup filled Indication

output reg [2:0] addr,

output reg [5:0] bal

);

integer total_amount_collected;

parameter coin_check = 3'd0;

parameter coffee_filling = 3'd1;

parameter coffee_filled = 3'd2;

parameter Tea_filling = 3'd3;

parameter Tea_filled = 3'd4;

parameter Milk_filling = 3'd5;

parameter Milk_filled = 3'd6;

reg [2:0] state,next_state;

reg cup_f_next;

always @(posedge clk)

begin

if (rst)

begin

state<= coin_check;

cup_f<=0;

end

else

begin

state<= next_state;

cup_f<=cup_f_next;

end

end

always @(state,coin,coin_valid)

begin

total_amount_collected = 0;

cup_f_next = 0;

addr = 0;

if (coin_valid) begin

case (state)

coin_check:

begin

if (coin==2'b00)

begin

next_state = coin_check;

addr =3'd1;

end

else if (coin==2'b01)

begin

next_state = coffee_filling;

total_amount_collected = 20;

end

else if (coin==2'b10)

begin

next_state =Tea_filling;

total_amount_collected =15;

end

else if (coin==2'b11)

begin

next_state = Milk_filling;

total_amount_collected = 25;

end

end

coffee_filling:

begin

addr =3'd3;

next_state = coffee_filled ;

end

coffee_filled :

begin

cup_f_next = 1;

addr =3'd2;

next_state = coin_check ;

end

Tea_filling :

begin

addr =3'd5;

next_state = Tea_filled ;

end

Tea_filled :

begin

cup_f_next = 1;

addr =3'd4;

next_state = coin_check ;

end

Milk_filling : begin

addr =3'd7;

next_state = Milk_filled;

end

Milk_filled :

begin

cup_f_next = 1;

addr =3'd6;

next_state = coin_check ;

end

default : next_state = coin_check;

endcase // case (state)

end

else

addr=3'd0;

end // always @ (state,next_state)

always@(posedge clk )

begin

if(rst)

bal = 0;

else

bal = bal+total_amount_collected;

end

endmodule

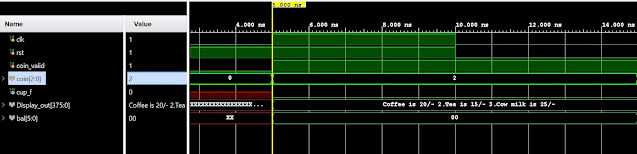

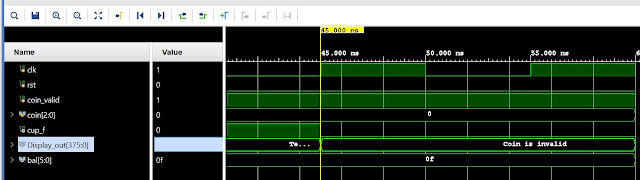

Simulation Results

Comments

Post a Comment