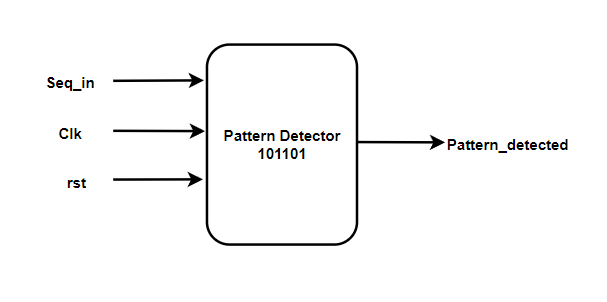

101101 Sequence Detector

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Weekendvlsi.blogspot.com

// Engineer: Weekendvlsi

//

// Create Date: 20-11-2021

// Design Name:

// Module Name: pattern_detector

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module pattern_detector(rst,clk,seq_in,pattern_detected);

output reg pattern_detected;

input clk, rst, seq_in;

reg [2:0] current_state;

reg [2:0] next_state;

parameter [2:0] state_0=3'b000;

parameter [2:0] state_1=3'b001;

parameter [2:0] state_2=3'b010;

parameter [2:0] state_3=3'b011;

parameter [2:0] state_4=3'b100;

parameter [2:0] state_5=3'b101;

always @(posedge clk, posedge rst) begin

if (rst)

current_state <= state_0;

else

current_state <= next_state;

end

always @(*) begin

next_state = current_state ;

case(current_state)

state_0:

if (seq_in) begin

next_state=state_1;

pattern_detected=1'b0;

end

else begin

next_state=state_0;

pattern_detected=1'b0;

end

state_1:

if (seq_in) begin

next_state=state_1;

pattern_detected=1'b0;

end

else begin

next_state=state_2;

pattern_detected=1'b0;

end

state_2:

if (seq_in) begin

next_state=state_3;

pattern_detected=1'b0;

end

else begin

next_state=state_0;

pattern_detected=1'b0;

end

state_3:

if (seq_in) begin

next_state=state_4;

pattern_detected=1'b0;

end

else begin

next_state=state_2;

pattern_detected=1'b0;

end

state_4:

if (seq_in) begin

next_state=state_1;

pattern_detected=1'b0;

end

else begin

next_state=state_5;

pattern_detected=1'b0;

end

state_5:

if (seq_in) begin

next_state=state_1;

pattern_detected=1'b1;

end

else begin

next_state=state_0;

pattern_detected=1'b0;

end

default:

begin

next_state=state_0;

pattern_detected=1'b0;

end

endcase

end

endmodule

Comments

Post a Comment