Program in HDL to generate nth Fibonacci number Where n is the input?

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Weekendvlsi.blogspot.com

// Engineer: Weekendvlsi

//

// Create Date: 27-11-2021

// Design Name:

// Module Name:

// Project Name: Printing nth Fibonacci

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module nth_fibonacci_num(

input clk,

input rst,

input [7:0] nth_fibonacci_req,

output [19:0] nth_fibonacci_value

) ;

reg [19:0] previous_value, present_value;

reg [7:0] ctr;

reg output_valid;

assign nth_fibonacci_value = present_value ;

always @( posedge clk) begin

if (rst) begin

previous_value <=0;

present_value <=1;

ctr <=1;

end

else begin

if (ctr == (nth_fibonacci_req-1)) begin

ctr <= ctr ;

present_value <= present_value ;

previous_value <= previous_value;

output_valid <= 1;

end

else begin

ctr <= ctr + 1;

present_value <= present_value + previous_value;

previous_value <= present_value;

output_valid <= 0;

end

end

end

always @(output_valid) begin

if(output_valid)

$display("N=%d, Nth Fibonacci number=%d",nth_fibonacci_req,nth_fibonacci_value);

end

endmodule

TEST BENCH:

module tb;

reg clk;

reg rst;

reg [7:0] nth_fibonacci_req;

wire [19:0] nth_fibonacci_value;

nth_fibonacci_num dut (

clk,

rst,

nth_fibonacci_req,

nth_fibonacci_value

) ;

always #5 clk=~clk;

initial begin

clk=0;rst=1;nth_fibonacci_req=0;

#10 rst=0;nth_fibonacci_req=10;

#100 $stop;

end

initial begin

$dumpfile("dump.vcd");

$dumpvars;

end

endmodule

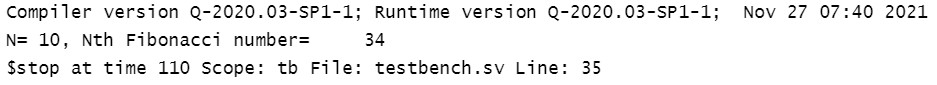

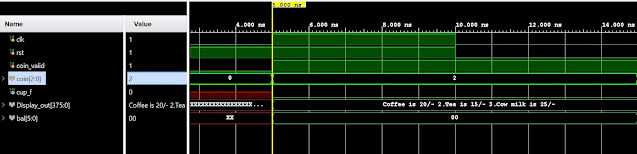

RESULT:

Comments

Post a Comment